I/O Designer FPGA--PCB辅助设计模块

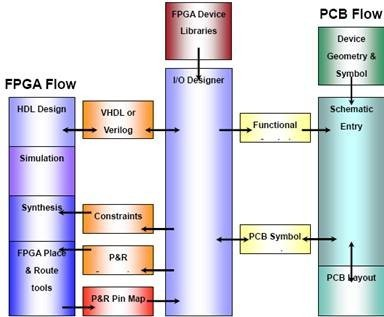

I/O Designer可为FPGA管脚分配、原理图符号创建及PCB中BGA封装网络优化提供了图形化的集成环境;连接FPGA管脚分配与PCB布局布线,使改进管脚分配变得轻而易举;可自动跟踪HDL源代码、FPGA管脚分配及PCB管脚网络信息的改变并进行同步更新提示;最大程度确保管脚分配信息在HDL设计、FPGA布局布线约束及PCB设计环境中的一致;支持各FPGA厂家的器件库,可根据需要指定或改变HDL源代码的实现器件;可根据管脚分配信息自动对比并更新HDL源代码、FPGA布局布线约束及BGA封装网络,避免了手工修改的烦琐与疏漏。

主要功能:

数据同步管理

在FPGA到PCB的设计流程里,HDL信号与FPGA管脚的映射信息必须严格保持一致。I/O Designer可以自动监测各个流程对管脚分配信息的修改,并提示其他流程及时同步更新,确保管脚分配信息在整个设计流程中的一致性。首先,I/O Designer支持手工或自动完成HDL信号到FPGA管脚的映射,并根据映射结果创建FPGA布局布线约束文件,然后结合HDL源文件生成用于板级设计的原理图符号、元件属性及管脚属性等信息;此外,I/O Designer还可以导入板级原理图或PCB设计中对管脚分配的修改操作,如管脚互换、逻辑门互换等,从而更新FPGA布局布线约束。

对于FPGA/PCB的同步设计,I/O Designer是一个功能强大且独一无二的解决方案,它为“FPGA布局布线-约束文件-板级PCB设计”提供了强有力的双向数据交换环境,设计者可以通过I/O Designer创建HDL信号、原理图符号、PCB布线规则、管脚电气信息、FPGA布局布线约束等多种数据,并传递给HDL、FPGA布局布线、PCB等各个设计流程,有效地实现了从概念设计、芯片设计到系统设计的无缝衔接。

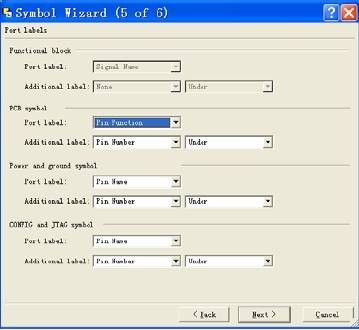

原理图符号

I/O Designer自带一个可订制的原理图符号(Symbol)与管脚(Pin)外形库,支持所有符合工业标准的Symbol与Pin的外形,设计者可以根据需要订制Symbol及Pin的形状。I/O Designer兼容多种文件格式的原理图与Symbol,可将自己创建的原理图及Symbol导出至Design Architect、Board Architect、DxDesigner、Design Capture、Design View等环境中,同时支持EDIF、XML等格式的原理图及Symbol文件的导入。

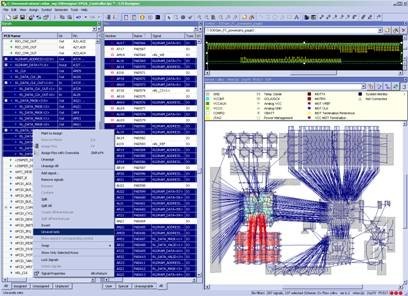

动态管脚分配与优化

I/O Designer为创建与优化FPGA管脚映射提供了简单直观的操作界面,设计者可以将信号或FPGA管脚从各自的表格中直接拖到Symbol管脚或FPGA封装的管脚上,以此实现信号到管脚的分配;也可以在封装窗口中根据导入带有网络飞线的PCB布局视图,为优化管脚分配提供参考。每一次修改了管脚分配后,I/O Designer都会实时更新PCB网络飞线的交叉情况,并自动更新FPGA布局布线约束文件。

ModSim DE

ModelSim DE提供了在层级上,经过验证的能力,包括基于断言的验证方法。

主要的产品特性:

l 本地编译,SKS技术

l VHDL,Verilog, PSL以及SystemVerilog设计和声明构造;SystemC等的选择

l 智能的,易于使用的具有Tcl界面的GUI

l 集成的项目管理,源码模板和向导。

l 波形查看和比对;目标,查看器和存储器窗口

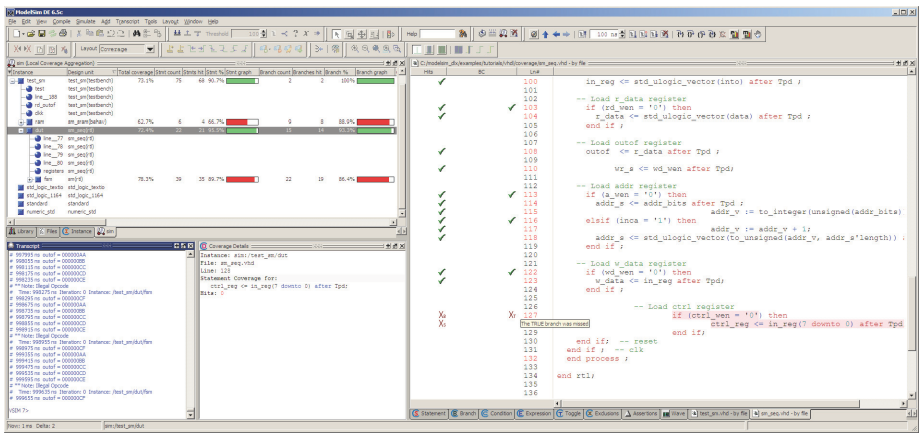

l 代码覆盖

l Xilinx SecureIP的标准支持

精致的FPGA验证

ModelSim DE 包装了一个具备史无前例水平的验证在成本效益优异的HDL仿真解决方案中。除了支持标准的HDLs,ModelSim DE 增加了设计品质和调试的能力。

ModelSim优秀的单核仿真器技术(SKS)使得VHDL和Verilog可以存在于一个设计中。其架构允许平台独立的与本地杰出的代码编译一起进行编译。

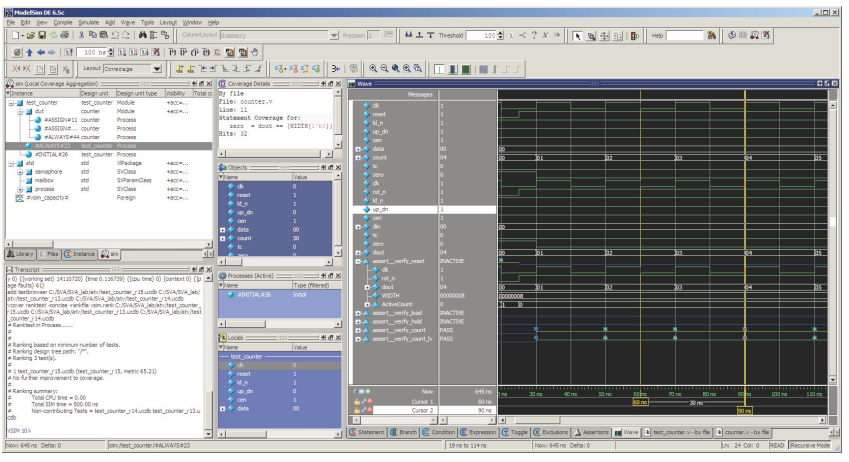

图形化的用户界面非常强大,一致且直观。所有的窗口自动的跟随其他窗口的活动而自动的进行更新。举个例子,在一个窗口架构中,选择一个设计区域,自动的更新源,信号,进程和变量窗口。你便可以编辑,重新编译,以及重新的进行仿真而不用离开ModelSim的环境。所有的用户界面操作可以被改写以及仿真也可以运行在批量或者交互式的模型中。

断言线程查看器显示了一个完整断言的评估,以识别每一个线程为什么通过或者失效。

ModelSim DE仿真行为级,RTL级和门级代码,包括VHDL VITAL和Verilog门库,随着标准延时格式(SDF)时序的提供。

基于断言的验证

基于断言的验证(ABV)通过白盒显示器的插入而提供了允许正确功能的积极监视。断言可以捕捉到积极测试中的错误,但是却不能捕捉黑盒的观察点;就像初级的输出。由于他们可以识别功能上的bug而更接近于其根本的原因,所以断言也可以实时的进行调试。时间将会节省很多,相对于回溯所导致的几个小时甚至一些天的延长。

ModelSim DE 使ABV通过System Verilog Assertion(SVA)的构造以及Property Specification Language(PSL)的支持。SVA和PSL断言都可以要么嵌入到HDL设计源代码中或者指定到单独的单元中,然后回到设计层次结构中的恰当的模块实例中。

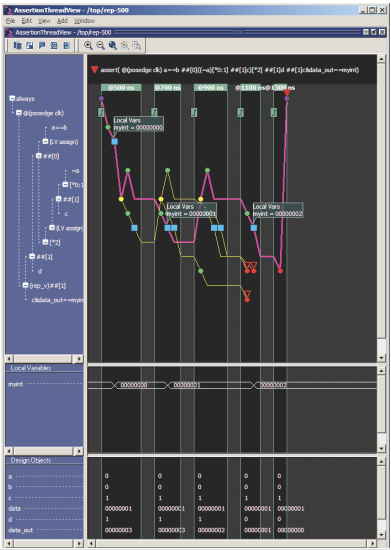

断言线程查看器和断言浏览器

当复杂的断言被触发,便可以通过检查在波形窗口中的仿真结果而查看失效的原因。断言也可以被记录到激活的地方的波形窗口中,成功的,失败的结果都很容易被识别。既然断言可以进行多线程并行的评估,ModelSim DE 包含了一个革新的断言线程查看器,其图形化的显示了一个激活的断言的完整的评估结果。在评估中,每一个线程都会显示出来,正如每一个布尔表达式在每一个线程的时序中的成功或者失败。本地的变量值也被显示为完整的断言调试环境。

每一个断言的统计信息能够在断言浏览器中被测试出来。断言统计信息包括激活的数量,成功,失败以及对于每一个断言的空洞的成功。

使用集成的代码覆盖,ModelSim DE 处理的设计已经被测试。

一个更加智能的GUI

一个更加智能的GUI高效的使用了桌面的资源。ModelSim DE 提供了一个直观的交互式图形界面(窗口,工具栏,菜单等)使其很容易查看并使用ModelSim的强大功能。这样的一个功能强大的GUI也易于进行使用和快速的精通。ModelSim通过了将Tcl用户界面合并到HDL仿真器中重新定义了其开放性。Tcl是一种对于控制和扩展应用的简单但功能强大的脚本语言。

ModelSim DE的GUI支持强大的设计调试和分析能力,以及项目和文件管理能力。

储存器窗口

存储器窗口允许直观并且灵活的进行查看和对设计存储器的调试。VHDL和Verilog 存储的内容被从源中提取出来并且显示在GUI上,其允许强大的搜索,填充,编辑,加载以及保存的功能。存储器窗口支持从文件或者常量,随机变量和计算值中预加载存储内容而保存耗时的测试平台的初始化部分,以加载存储器的值。所有的功能都可以通过命令行的方式来实现,也允许通过脚本进行使用。

咨询热线

专业客服为您解疑答惑